研究者らは、相変化メモリという技術の一般市場に向けた実用化に大きく近づいている。相変化メモリにより、将来のコンピュータの接続方法は変わることになるかもしれない。

Intelと、同社とSTMicroelectronicsのフラッシュメモリを専門とする合弁企業であるNumonyxは米国時間10月28日、新しい種類の相変化メモリチップを構築したと発表した。小型化と大容量化という同技術の利点を実現することができると両社は期待している。

64Mビットという容量自体は、新しいものではない。Numonyxは2006年に、128Mビットのデバイスを発表しており、サムスンは2009年9月、512Mビットのチップを製造中であると述べている。しかし今回重要なのは、長きにわたって練られてきた構想を実用化した2つの主要な技術進歩である。

1つめは、チップ内にワイヤグリッドを構成し、コンピュータが、6400万個のメモリセルの1つ1つに対する1または0の書き込みを容易に制御できるようにしたことである。2つめは、製造プロセスにおいて複数のレイヤを上下に積層可能とすることにより、同じ面積により高密度にメモリを集積できるようにしたことである。

コンピュータへの数値の保存は、かなり昔から実現されている。ではなぜ、特定の種類のガラスの分子状態を変化させることにより、1または0を記録する相変化メモリが、それほど大きな意味を持つのだろうか?

簡単に言うと、このメモリは、従来型のコンピュータメモリの高速性と、フラッシュメモリの低コスト、低消費電力、大容量という特長を併せ持つことができるかもしれないのだ。高速メモリを大量に搭載することができれば、コンピュータのハードウェアおよびソフトウェアを簡素化できる可能性がある。現状では、性能と容量のトレードオフが存在するストレージ技術の階層に対処しなければならない。

今日のOSは、重要な情報を絶えずメモリに保存し続けなければならない。古い情報は、ハードドライブに格納された「仮想メモリ」か、最近では階層の中間層に位置する、フラッシュメモリで構成されたソリッドステートディスクへと退避する。何をどこに保存するかを決定する処理は複雑であり、優先度は瞬間ごとに変化する。

Intelのメモリ技術開発担当ディレクターであるAl Fazio氏は28日、この技術について、「Intelでは、将来的なメモリを可能にする上で、これを重要なマイルストーンだと考えている。メモリとストレージの要素を組み合わせ、こうした技術を1つのメモリタイプに落とし込めるかもしれない。この研究は、実現に向けて非常に有望だ」と語った。

相変化メモリはまた、現在のメモリ技術をさらに小型化する際の問題をうまく回避できるかもしれない。そのほかにも、電力消費を抑えることで、廃熱の削減やバッテリ寿命の延長につながる可能性もある。

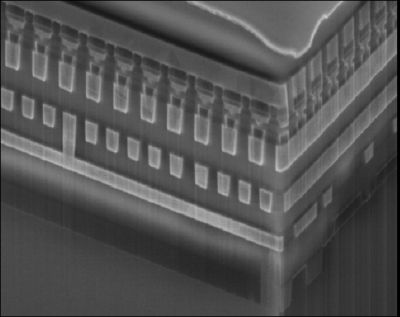

この画像は、従来型のCMOSマイクロチップ上に構築された相変化メモリを示したものである。メモリセルは、チップに接続されたワイヤの行と列を使って制御することができる。

この画像は、従来型のCMOSマイクロチップ上に構築された相変化メモリを示したものである。メモリセルは、チップに接続されたワイヤの行と列を使って制御することができる。

この記事は海外CBS Interactive発の記事を朝日インタラクティブが日本向けに編集したものです。原文へ

CNET Japanの記事を毎朝メールでまとめ読み(無料)

心と体をたった1分で見える化

心と体をたった1分で見える化

働くあなたの心身コンディションを見守る

最新スマートウオッチが整える日常へ

プライバシーを守って空間を変える

プライバシーを守って空間を変える

ドコモビジネス×海外発スタートアップ

共創で生まれた“使える”人流解析とは

ひとごとではない生成AIの衝撃

ひとごとではない生成AIの衝撃

Copilot + PCならではのAI機能にくわえ

HP独自のAI機能がPCに変革をもたらす

メルカリが「2四半期連続のMAU減少」を恐れない理由--日本事業責任者が語る【インタビュー】

メルカリが「2四半期連続のMAU減少」を恐れない理由--日本事業責任者が語る【インタビュー】

なぜPayPayは他のスマホ決済を圧倒できたのか--「やり方はADSLの時と同じ」とは

なぜPayPayは他のスマホ決済を圧倒できたのか--「やり方はADSLの時と同じ」とは

AIが通訳するから英語学習は今後「オワコン」?--スピークバディCEOの見方は

AIが通訳するから英語学習は今後「オワコン」?--スピークバディCEOの見方は

パラマウントベッド、100人の若手が浮き彫りにした課題からCVCが誕生

パラマウントベッド、100人の若手が浮き彫りにした課題からCVCが誕生

野村不動産グループが浜松町に本社を「移転する前」に実施した「トライアルオフィス」とは

野村不動産グループが浜松町に本社を「移転する前」に実施した「トライアルオフィス」とは

「ChatGPT Search」の衝撃--Chromeの検索窓がデフォルトで「ChatGPT」に

「ChatGPT Search」の衝撃--Chromeの検索窓がデフォルトで「ChatGPT」に

「S.RIDE」が目指す「タクシーが捕まる世界」--タクシー配車のエスライド、ビジネス向け好調

「S.RIDE」が目指す「タクシーが捕まる世界」--タクシー配車のエスライド、ビジネス向け好調

物流の現場でデータドリブンな文化を創る--「2024年問題」に向け、大和物流が挑む効率化とは

物流の現場でデータドリブンな文化を創る--「2024年問題」に向け、大和物流が挑む効率化とは

「ビットコイン」に資産性はあるのか--積立サービスを始めたメルカリ、担当CEOに聞いた

「ビットコイン」に資産性はあるのか--積立サービスを始めたメルカリ、担当CEOに聞いた

培養肉の課題は多大なコスト--うなぎ開発のForsea Foodsに聞く商品化までの道のり

培養肉の課題は多大なコスト--うなぎ開発のForsea Foodsに聞く商品化までの道のり

過去の歴史から学ぶ持続可能な事業とは--陽と人と日本郵政グループ、農業と物流の課題解決へ

過去の歴史から学ぶ持続可能な事業とは--陽と人と日本郵政グループ、農業と物流の課題解決へ

通信品質対策にHAPS、銀行にdポイント--6月就任のNTTドコモ新社長、前田氏に聞く

通信品質対策にHAPS、銀行にdポイント--6月就任のNTTドコモ新社長、前田氏に聞く

「代理店でもコンサルでもない」I&COが企業の課題を解決する

「代理店でもコンサルでもない」I&COが企業の課題を解決する