有線およびデータ センター インターコネクト向けに次なるイーサネット展開を加速するデバイスを提供

[画像1: リンク ]

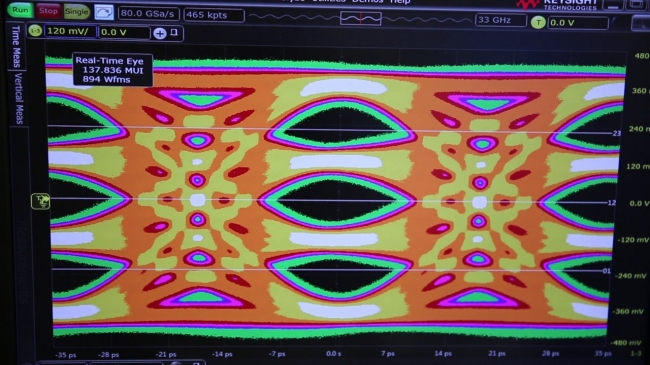

ザイリンクス社 (本社 : 米国カリフォルニア州サンノゼ、NASDAQ : XLNX) は 5 月 17 日 (米国時間)、56G PAM4 トランシーバー テクノロジを、業界をリードする 16nm Virtex(R) UltraScale+™ FPGA と統合した製品として提供することを発表した。すでに量産出荷の実績がある 16nm FinFET+ FPGA ファブリックを基盤として構成されたこれらのデバイスは、Virtex 製品ラインを拡張して次なるイーサネット展開を推進するとともに、次世代のバックプレーン、光ファイバー通信、高性能インターコネクトへ既存システムを円滑に移行させる。

[画像2: リンク ]

Virtex UltraScale+ FPGA に 56G PAM4 トランシーバー テクノロジを統合したこれらのデバイスは、有線通信やデータ センター、無線バックホール アプリケーションを対象としている。これらのデバイスの使うことにより、56G+ ラインレートでのデータ転送の物理的な限界を突破することで、既存インフラの帯域幅を 2 倍にすることが可能となる。

ザイリンクスの SerDes テクノロジ グループ担当バイス プレジデントであるケン チャン (Ken Chang) は、「ザイリンクスは、56G PAM4 を 16nm FPGA へ統合することにより、これからもトランシーバー テクノロジをリードします。これらの新しいデバイスは実績のある FPGA を基盤として構成されており、間もなく展開される光ファイバー通信や、バックプレーンにおける広範なエコシステムとも調和が取れています」と述べている。

ザイリンクスは 2016 年に初めて、16nm プログラマブル デバイス上での 56G PAM4 トランシーバー テクノロジのデモンストレーションを実施した。今回の発表は、2016 年のデモンストレーションに続いて、ザイリンクスのトランシーバー テクノロジにおけるリーダーシップの節目を示すものである。詳細は、ザイリンクスの 56G PAM4 テクノロジのデモンストレーションをご覧いただき、また最寄りの販売代理店へお問い合わせいただきたい。

ザイリンクスについて

ザイリンクスは、All Programmable FPGA、SoC、MPSoC、RFSoC、3D IC の世界的なリーディング プロバイダーである。ソフトウェア定義でハードウェアが最適化されたアプリケーションを可能にすることによって、クラウド コンピューティング、5G ワイヤレス、エンベデッド ビジョンおよびインダストリアル IoT などの分野に飛躍的進歩をもたらす。詳しい情報は、ウェブサイト japan.xilinx.com で公開している。

※ザイリンクスの名称およびロゴ、Artix、ISE、Kintex、Spartan、Virtex、Vivado、Zynq、その他本プレスリリースに記載のブランド名は米国およびその他各国のザイリンクスの登録商標または商標です。その他すべての名称は、それぞれの所有者に帰属します。

■下記のザイリンクス株式会社ウェブサイトもご参照ください。

・トップページ : リンク

・プレスリリース (日本語) : リンク

・このリリースの全文は次の URL を参照のこと :

リンク

プレスリリース提供:PR TIMES リンク

御社のプレスリリース・イベント情報を登録するには、ZDNet Japan企業情報センターサービスへのお申し込みをいただく必要がございます。詳しくは以下のページをご覧ください。